ご存じの通り、Apple Silicon「M1」を搭載したMacが発売された。この連載の担当編集である松尾氏も早速入手されたそうで何よりである。現状のM1は、ある意味「拡張性を犠牲にして性能を優先した」構成であり、今後拡張性が求められるようになっていくと、いろいろ厳しいシーンも出てくるとは思うが、それをどう(CPUコアのアーキテクチャだけでなく、SoCのアーキテクチャも含めて)解決しながら性能を上げていくかが楽しみである。

さてこの連載の最後に、そういうApple Siliconの先にあるものを少し考察してみたい。結論からいえば、Appleは既にApple ISA(Instruction Set Architecture)の策定作業にかかっていると思う。それが世の中に登場するのはまだだいぶ先だと思うし、動向次第では世に出ずに終わる可能性も多少はあるが、そうした作業をやってないというのは、まずありえないと思う。以下、その理由を述べたい。

話はいきなり飛ぶが、昨今のプロセッサのマーケットでは「いかにヘテロジニアス環境をうまく動かすか」が焦点になってきている。Intelですら、という言い方もどうかとは思うが、もはやCPUだけでは十分な性能を確保できないと理解しているはずだ。それゆえ、Habana LabsとMovidiusを買収してAIの学習と推論に適したプロセッサを手に入れ、AMDからラジャ・コドゥリ氏を招いて新しいXeファミリーのGPUを開発し、Alteraを買収してFPGAを手に入れ、そしてこれらを横断的に扱えるようにするための環境としてoneAPIやOpenVINOといったAPIを提供しようとしている。

これは別にIntelだけではない。AMDは強力なGPUを持っているし、QualcommやMediaTekといったモバイルSoCベンダーもCPUだけでなくGPUやNPUなど複数種類のプロセッサを組み合わせるようになっている。これはAppleも同じことだ。

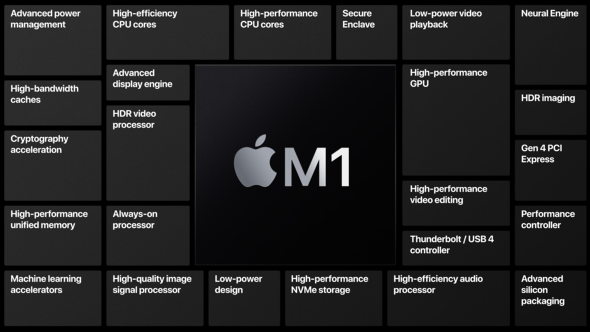

M1にしても

- 高性能なCPUコア

- 高効率(=性能は低いが省電力)なCPUコア

- 高性能なGPUコア

- Neural Engine

- HDR Video Processor

- 省電力なVideo Playback(Accelerator)

- 高性能なVideo Editing(Accelerator)

- 高精度なISP(Image Signal Processor)

- 高効率なAudio Processor

- Security Enclave(セキュリティドメイン:Root of Trustその他を実装)

の組み合わせになっているのが分かる。

ここでProcessorとAcceleratorの違いは、自分で処理を実行できるか、外から制御が必要かである(Acceleratorは、CPUから実行開始のリクエストを受けて処理を行い、終わると待機状態に戻る。Processorは自分でプログラムを読み込んでどんどん実行できる)。

ヘテロジニアス環境の課題

問題なのは、Acceleratorもそうだが、Processorに関しては全部命令がバラバラであり、しかもプロセッサ間の同期を取るメカニズムがまちまちであることだ。

例えばGPU。Appleは2014年にOpenGLやOpenCLに代わるものとしてMetalを導入した。使い方は?というと(語弊を覚悟でいえば)よくあるAPIベースの呼び出しであって、プログラムから見ればデバイスのオブジェクトを作り、そのオブジェクトに対して操作を行うという形になる。これ、内部的にはおそらくPCI Expressのデバイスドライバの形を取ってGPUに対して基本的な操作を行う(GPUとCPUの間にCache Coherencyがあるかどうかは不明)形になっていると思われるのだが、これがオーバーヘッドを生んでいるのは疑う余地もない。Neural Processorもそうだし、ISPやVideo Processorなども当然同じであろう

ヘテロジニアス環境の理想で言えば、CPUとGPU、NPUその他が並列に並び、1つのメモリをCache CoherencyにUnified Accessできることが望ましいし、長期的には命令セットが共通化きれればより好ましい。加えて、とりあえず同期のメカニズムそのものを何とかしないといけない。現状の実装方法はいろいろだが、ポピュラーなのは、

- GPUやNPUが処理が終わったら、CPUに対して割り込みを掛ける

- 割り込みを受け取ったCPUは現在の処理を一端棚上げにして、割り込み処理ルーティン(ISR:Interrupt Service Routine)を起動する

- ISR内部では割り込みの内容を判断し、関係するThreadに対して通知を行う処理を行い(この時点ではまだ処理を積んだだけで通知そのものは行われない)、ISRを抜ける。

- CPUは先ほど棚上げにした処理を再開する。

- そのうちに関係するThreadが実行可能になると、先にISRで積んだ「通知を行う処理」が実行され、そのThreadにGPUやNPUが処理を完了したことが通知される。

という気の長い方式である。

実は外部デバイスを利用すると、大体が割り込みを使って同期を取る必要があり、この割り込みのハンドリングが非常に大きなオーバーヘッドであるために、煩雑に同期を取るようなケースではどんどん性能が落ちていくという欠点がある。ヘテロジニアス環境の最大のネックがここにある。

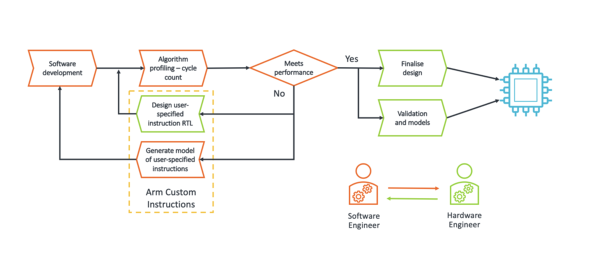

こうした課題への対応を、実はArmは既に始めている。MONOistに書いた記事、Arm「Custom Instruction」の衝撃、RISC-Vへの徹底抗戦を貫くのタイトルにも入っているCustom Instructionがそれだ。もちろん現状はCortex-Mベースの製品のみの対応だし、あくまでMCUのダイに収まる範囲のAccelerator/Coprocessorが対応であるが、理屈上はこれを拡張すればCortex-Aに適応することは難しくないし、専用ポートを用意して外部のGPUやNPUを同期させることも不可能ではない(Cortex-AのDynamIQには、このためのACPというポートもある)。RISC-Vは既にこれを実現しているし、MIPSやPowerPCでもこうしたCustom Instructionのサポートがあった。ただArmはCortex-Aグレードへの適用時期はまだ公開していない。

ではAppleは、ArmがこうしたCustom Instructionsに対応するのを待つかの? とりあえずは待たざるを得ない(というか、水面下でガンガンリクエストを出しているはず)だろうが、あまりそれが遅い or Appleの望むような仕様にならなかった場合に備えて「Plan B」を用意するというのは別に不思議ではない。

Appleの「Plan B」、Apple ISAとRosetta 3

もう一つ、Armの命令セットで不都合があるのは、NVIDIAの買収に絡む話である。NVIDIAのジェンセン・ファンCEOはArm買収に際し、「将来のArmのIPでCUDAが利用できるようになる」という見通しを述べている(この辺りは「Arm買収、本当にできるの? NVIDIAの真意とは」で書いたので繰り返さない)。問題はAppleの立場で考えた時、果たしてCUDAをサポートするArm命令はどう見えるだろうか、ということだ。

こうした状況を考えると、既にAppleはArm ISAの次になるものの検討や実際に仕様策定の作業を開始しているだろうと筆者は確信している。そして、それはRISC-Vではないだろう。Appleは既に独自のアーキテクチャに基づくSiliconとSoftware Platform、そこに向けた開発環境及びエコシステムパートナーを既に抱えている。これはRISC-V陣営が今もって欲しており、ただまだ十分からはかなり遠い状況にあるものだ。つまりAppleはRISC-Vに参加して得られるもの以上の環境を既に自分自身で構築しており、参加するメリットが皆無である。むしろAppleの好き勝手にISAを策定できない、というデメリットだけが残る結果になりかねない。

そもそもRISC連載「RISCの生い立ちからRISC-Vまでの遠い道のり」で説明してきたように、命令セットそのものの構築は、超優秀なエンジニアが数人程度いれば可能である。

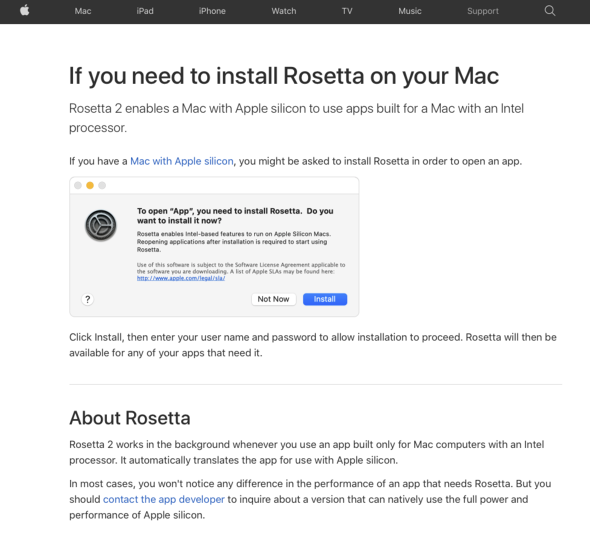

それをSiliconにするのには相応の数のエンジニアが必要だが、既にA14やApple M1を現実に構築しているAppleならば当然可能である。ちなみにこれはMacだけでなくiOSデバイスも同じである。現状のApple M1の上で動くRosetta 2の性能を鑑みれば、将来のiOSデバイス上でRosetta 3(仮)を動かすのは難しいことではない。まずはRosetta 3(仮)の上で既存のiOSアプリケーションを稼働させ、数年の間にApple ISAネイティブに移行させる、というのは無理がないだろう。

もちろんこれが登場するのはずいぶん後になるだろう。プラットフォームの転換には数年間掛かる。実際Apple自身、今後2年間はIntel MacとArm Macが併売されると明言している訳で、切り替えが完全に終わり、Intel MacのOSがサポートされなくなるまでにはあと5年かそこらはかかるだろう。切り替えが行われるとすれば、その後である。

そもそも直近、Appleの開発陣は、M2(仮)とかM3(仮)の設計作業で忙しいだろう。M1はある意味従来のiPhone/iPadと同じ熱容量の設計であり、「ほどほどの消費電力で相対的に高い」性能は出せるが、「電力をフルに消費してブン回せる」設計にはなっていない。

かつてAppleが買収したP.A.Semi(連載で説明した、ダニエル・W・ドバープール氏率いる一団だ)はこうした設計が得意(なにせサーバマーケット向けのチップをSiByteとP.A.Semiで作っていた)なのだが、これは12年も前の話。ジム・ケラー氏が抜けたのも8年前であり、現状でP.A.Semi時代のエンジニアがどのくらい残っているかは不明である。

なので仮にサーバ向けチップを作るノウハウがほぼ失われたと仮定すると、やはり設計(特に物理設計)には半年以上かかる気がする。この辺りが一段落するのは2021年後半だろうか? その辺りから、Apple ISAを実装したテストチップというかプロトタイプがぼちぼちと試作を始めるのではないかと思う。

プロトタイプである程度の性能が出ることが確認できたら、macOSやiOSの移植がスタートし、アプリケーションの動作確認を行い、移行ツールや開発環境のサポートを追加して、という具合に用意に数年を要するだろう。後は市場の動向などを見ながら、どこかのタイミングでApple ISAに切り替える発表をするだけだ。個人的な見通しで言えば、2020年代はArm Macが続くかもしれない。ただ2030年代はもうArm Macではないような気がする。

Appleというのは、現状では唯一「垂直統合」を成し遂げたコンピュータベンダーになった。かつてはIBMにしても国内のコンピュータメーカーにしても、独自のアーキテクチャと命令セットを持つマシンを自社で製造、ソフトウェアも自社提供という形になっていた。それが時代が経るごとにどんどん垂直統合から水平分散に代わっていき、アーキテクチャのベンダー、シリコンのベンダー、ソフトウェアのベンダー、と複数のベンダーがまとまってソリューションを提供する形に変わっていった。

唯一Appleだけがこの流れに逆らう形で垂直統合を進めるという、歴史的に見ると非常に稀有な存在になっている。仮にApple ISAが実現した場合、残されるのはFabである。例えば2030年代に入って、破綻したIntelのFabをAppleが買収して自社のSilicon製造を行う、なんてシナリオは昨今の業界の動向を見ていると、あながち荒唐無稽とは言い切れない。さて、どうなるだろうか?

関連記事

"最終" - Google ニュース

November 25, 2020 at 05:05AM

https://ift.tt/3fHT7A5

最終回:Apple Siliconがやってきた そのさらに先、「Apple ISA」への遠い道のり - ITmedia

"最終" - Google ニュース

https://ift.tt/2TBKrCd

Shoes Man Tutorial

Pos News Update

Meme Update

Korean Entertainment News

Japan News Update

No comments:

Post a Comment